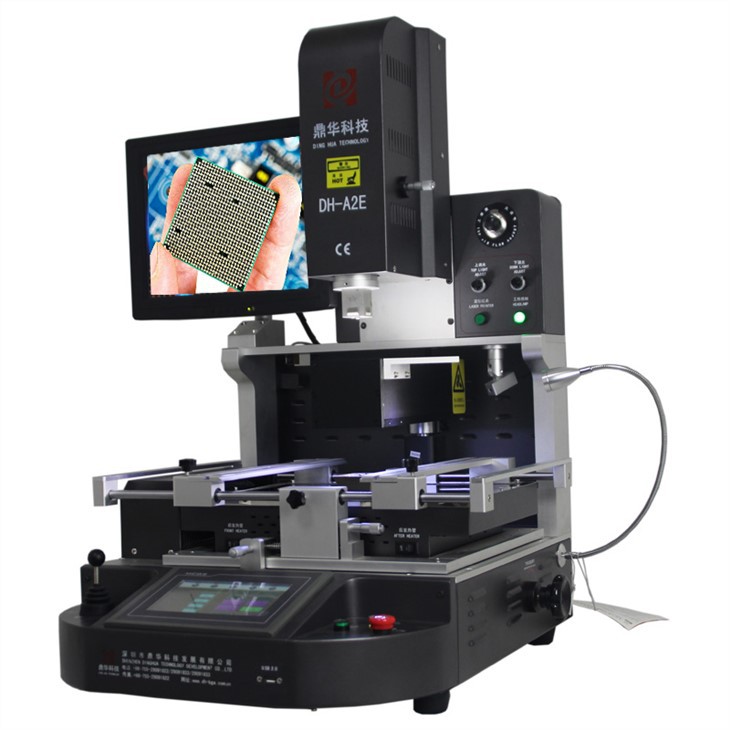

অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশন

মোবাইল, ল্যাপটপ, কম্পিউটার, টিভি, এয়ার কন্ডিশনার ইত্যাদির মাদারবোর্ডের জন্য চিপ-লেভেল মেরামতে ব্যাপকভাবে ব্যবহৃত হয়। এটি মেরামতের উচ্চ সফল হার এবং উচ্চ মাত্রার অটোমেশন এবং প্রচুর মানুষের প্রচেষ্টা বাঁচায়। আমরা এই মেশিনের পেশাদার প্রস্তুতকারক এবং এই মেশিনগুলি স্টকে উপলব্ধ রয়েছে।

বিবরণ

অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশন

1.অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশনের আবেদন

কম্পিউটারের মাদারবোর্ড, স্মার্ট ফোন, ল্যাপটপ, ম্যাকবুক লজিক বোর্ড, ডিজিটাল ক্যামেরা, এয়ার কন্ডিশনার, টিভি এবং অন্যান্য ইলেকট্রনিক

চিকিৎসা শিল্প, যোগাযোগ শিল্প, অটোমোবাইল শিল্প, ইত্যাদি থেকে সরঞ্জাম

বিভিন্ন ধরণের চিপগুলির জন্য উপযুক্ত: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED চিপ।

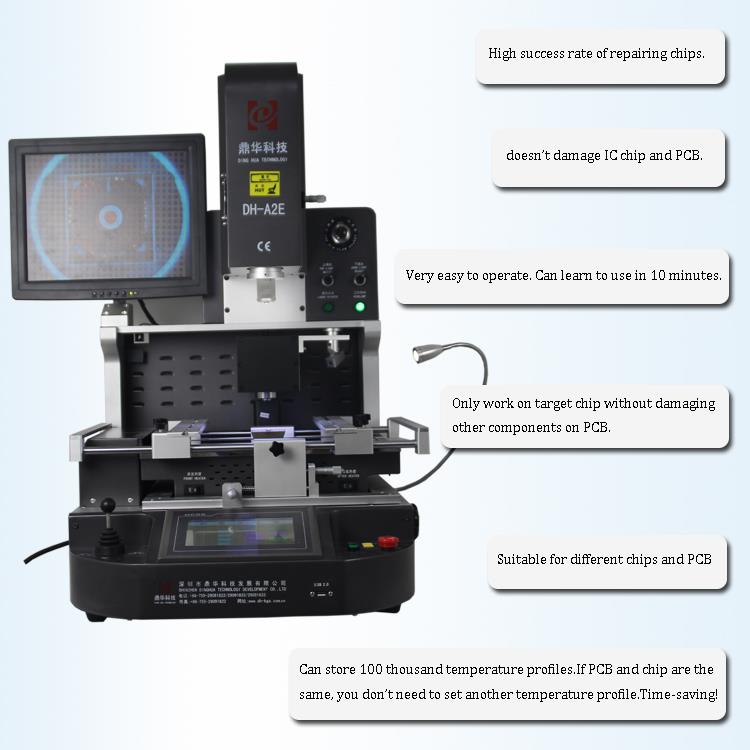

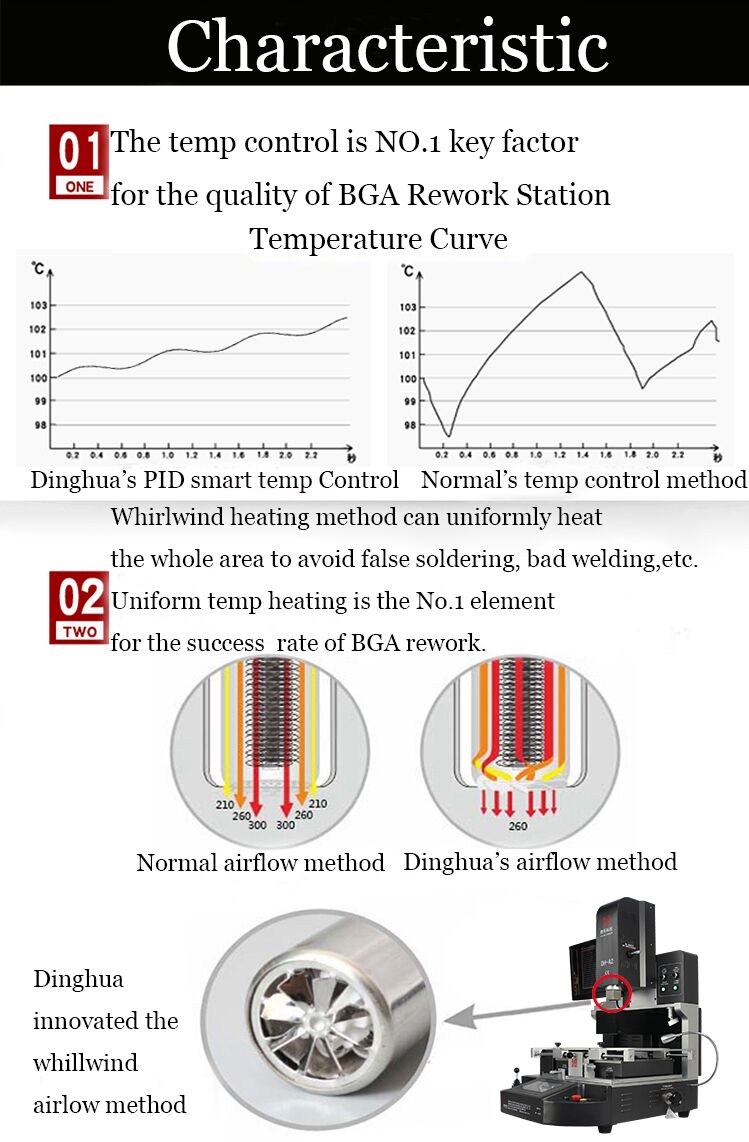

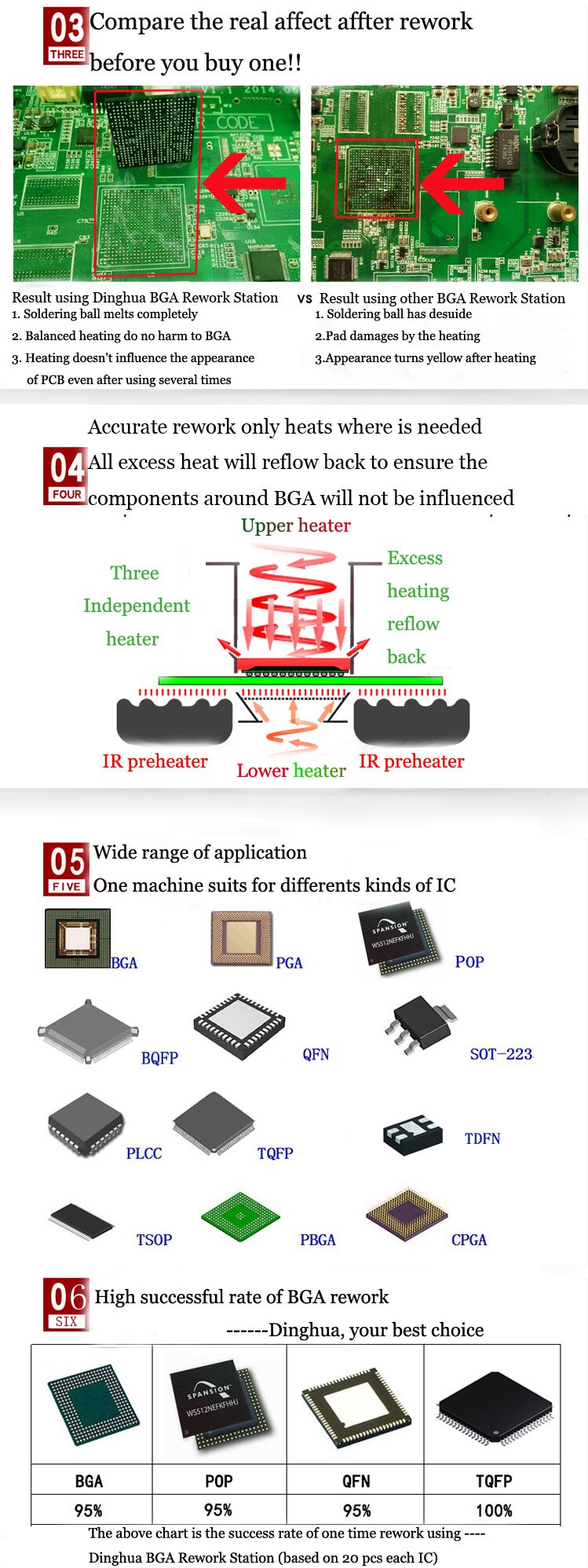

2. অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশনের পণ্য বৈশিষ্ট্য

•চিপ-স্তরের মেরামতের উচ্চ সফল হার। ডিসোল্ডারিং, মাউন্টিং এবং সোল্ডারিং প্রক্রিয়া স্বয়ংক্রিয়।

• প্রতিটি সোল্ডারিং জয়েন্টের সুনির্দিষ্ট প্রান্তিককরণ অপটিক্যাল অ্যালাইনমেন্ট সিসিডি ক্যামেরার মাধ্যমে নিশ্চিত করা যেতে পারে।

• সুনির্দিষ্ট তাপমাত্রা নিয়ন্ত্রণ 3টি স্বাধীন গরম করার জায়গা দিয়ে নিশ্চিত করা যেতে পারে। মেশিন সেট এবং সংরক্ষণ করতে পারেন

তাপমাত্রা প্রোফাইলের 1 মিলিয়ন।

• মাউন্টিং হেডে বিল্ড-ইন ভ্যাকুয়াম ডিসোল্ডারিং সম্পন্ন করার পর স্বয়ংক্রিয়ভাবে BGA চিপ পিক আপ করে।

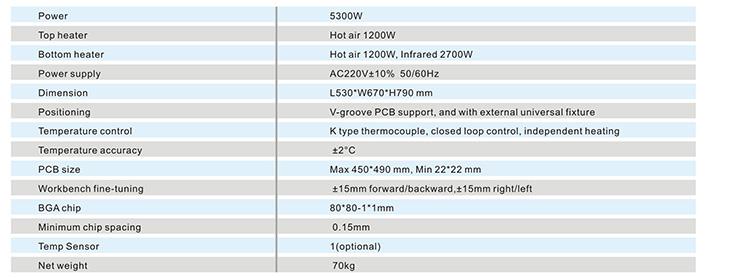

3. অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশনের স্পেসিফিকেশন

4. অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশনের বিশদ বিবরণ

সিসিডি ক্যামেরা (সুনির্দিষ্ট অপটিক্যাল অ্যালাইনমেন্ট সিস্টেম); 2. HD ডিজিটাল ডিসপ্লে; 3. মাইক্রোমিটার (চিপের কোণ সামঞ্জস্য করুন);

4.3 স্বাধীন হিটার (গরম বাতাস এবং ইনফ্রারেড); 5. লেজার পজিশনিং; 6. এইচডি টাচ স্ক্রিন ইন্টারফেস, পিএলসি নিয়ন্ত্রণ;

7. LED হেডল্যাম্প; 8.জয়স্টিক নিয়ন্ত্রণ।

5. কেন আমাদের অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশন বেছে নিন?

6. অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশনের সার্টিফিকেট

7. অটো অপটিক্যাল বিজিএ রিওয়ার্ক স্টেশনের প্যাকিং ও চালান

8. প্রায়শই জিজ্ঞাসিত প্রশ্নাবলী

কিভাবে চিপ পরীক্ষা করতে?

প্রাথমিক সিস্টেম-স্তরের চিপ পরীক্ষা

SoC গভীর সাবমাইক্রন প্রক্রিয়ার উপর ভিত্তি করে, তাই নতুন Soc ডিভাইস পরীক্ষা করার জন্য একটি সম্পূর্ণ নতুন পদ্ধতির প্রয়োজন। কারণ প্রতিটি কার্যকরী উপাদান

এর নিজস্ব পরীক্ষার প্রয়োজনীয়তা রয়েছে, ডিজাইন ইঞ্জিনিয়ারকে অবশ্যই ডিজাইন প্রক্রিয়ার প্রথম দিকে একটি পরীক্ষা পরিকল্পনা করতে হবে।

SoC ডিভাইসের জন্য ব্লক-বাই-ব্লক টেস্ট প্ল্যান বাস্তবায়িত করা আবশ্যক: যুক্তি পরীক্ষার জন্য সঠিকভাবে কনফিগার করা ATPG টুলস; সংক্ষিপ্ত পরীক্ষার সময়; নতুন উচ্চ গতির

ফল্ট মডেল এবং একাধিক মেমরি বা ছোট অ্যারে পরীক্ষা। উত্পাদন লাইনের জন্য, ডায়গনিস্টিক পদ্ধতিটি কেবল ত্রুটি খুঁজে পায় না, তবে পৃথক করে

কাজ নোড থেকে ত্রুটিপূর্ণ নোড. উপরন্তু, পরীক্ষার সময় বাঁচাতে যখনই সম্ভব টেস্ট মাল্টিপ্লেক্সিং কৌশল ব্যবহার করা উচিত। উচ্চ ক্ষেত্রের মধ্যে

ইন্টিগ্রেটেড আইসি টেস্টিং, ATPG এবং IDDQ-এর পরীক্ষাযোগ্য ডিজাইন কৌশলগুলির একটি শক্তিশালী ফল্ট বিচ্ছেদ প্রক্রিয়া রয়েছে।

অন্যান্য প্রকৃত পরামিতি যা আগে থেকে পরিকল্পনা করা দরকার তার মধ্যে রয়েছে স্ক্যান করা পিনের সংখ্যা এবং প্রতিটি পিনের শেষে মেমরির পরিমাণ।

সীমানা স্ক্যানগুলি SoC-তে এমবেড করা যেতে পারে, তবে বোর্ড বা মাল্টি-চিপ মডিউলগুলিতে আন্তঃসংযোগ পরীক্ষার মধ্যে সীমাবদ্ধ নয়।

যদিও চিপের আকার কমছে, একটি চিপ এখনও লক্ষ লক্ষ থেকে 100 মিলিয়ন ট্রানজিস্টর প্যাক করতে পারে এবং পরীক্ষার মোডের সংখ্যা অভূতপূর্বে বেড়েছে

মাত্রা, দীর্ঘ পরীক্ষার চক্রের ফলে। এই সমস্যা পরীক্ষা করা যেতে পারে। মোড কম্প্রেশন সমাধানের জন্য, কম্প্রেশন অনুপাত 20 শতাংশ থেকে 60 শতাংশে পৌঁছাতে পারে। আজকের বড় মাপের জন্য

চিপ ডিজাইন, ধারণক্ষমতার সমস্যা এড়াতে, 64-বিট অপারেটিং সিস্টেমে চলতে পারে এমন পরীক্ষার সফ্টওয়্যার খুঁজে বের করা প্রয়োজন৷

উপরন্তু, পরীক্ষা সফ্টওয়্যার গভীর সাব-মাইক্রোন প্রক্রিয়া এবং ক্রমবর্ধমান ফ্রিকোয়েন্সি দ্বারা সৃষ্ট নতুন পরীক্ষার সমস্যার সম্মুখীন হয়। অতীতে, এটিপিজি পরীক্ষার মোডের জন্য

স্ট্যাটিক ব্লকিং ফল্ট পরীক্ষা করা আর প্রযোজ্য ছিল না। ঐতিহ্যগত সরঞ্জামগুলিতে কার্যকরী নিদর্শন যোগ করা নতুন ত্রুটিগুলি খুঁজে পাওয়া কঠিন করে তুলেছে। একটি ভাল পদ্ধতির হয়

কোন ত্রুটি সনাক্ত করা যাবে না তা নির্ধারণ করতে অতীতের কার্যকরী মোড গোষ্ঠীগুলিকে শ্রেণীবদ্ধ করুন এবং তারপরে এই অনুপস্থিত ফল্ট প্রকারগুলি ক্যাপচার করতে একটি ATPG মোড তৈরি করুন৷

ডিজাইনের ক্ষমতা বাড়ার সাথে সাথে প্রতি ট্রানজিস্টরের পরীক্ষার সময় হ্রাস পায়, গতি-সম্পর্কিত সমস্যাগুলি খুঁজে পেতে এবং সার্কিটের সময় যাচাই করার জন্য, একটি সিঙ্ক্রোনাস পরীক্ষা পদ্ধতি

নিযুক্ত করা আবশ্যক। সিঙ্ক্রোনাস টেস্টিংয়ে ক্ষণস্থায়ী মডেল, পথ বিলম্ব এবং IDDQ সহ একাধিক ফল্ট মডেল অন্তর্ভুক্ত করতে হবে।

শিল্পের কিছু কোম্পানি বিশ্বাস করে যে ব্লকিং, কার্যকরী, এবং ক্ষণস্থায়ী/পথ বিলম্বের ত্রুটিগুলিকে একত্রিত করা সবচেয়ে কার্যকর পরীক্ষার কৌশল হতে পারে। গভীর জন্য

সাবমাইক্রন চিপস এবং উচ্চ ফ্রিকোয়েন্সি অপারেশন, ক্ষণস্থায়ী এবং পথ বিলম্ব পরীক্ষা আরও গুরুত্বপূর্ণ।

পরীক্ষার কোর সিঙ্ক্রোনাইজ করার সময় ATE নির্ভুলতার সমস্যা সমাধান করতে এবং খরচ কমাতে, একটি নতুন পদ্ধতি খুঁজে বের করা প্রয়োজন যা এর ইন্টারফেসটিকে সহজ করে তোলে

পরীক্ষা ডিভাইস (ক্ষণস্থায়ী এবং পথ বিলম্ব পরীক্ষার জন্য পরীক্ষা ডিভাইস ইন্টারফেসে সঠিক ঘড়ি প্রয়োজন), এটি নিশ্চিত করে যে পরীক্ষার সময় সংকেত যথেষ্ট সঠিক।

যেহেতু SoC মেমরি ব্লকে ম্যানুফ্যাকচারিং ত্রুটির উচ্চ সম্ভাবনা রয়েছে, তাই মেমরি BIST-এর একটি ডায়াগনস্টিক ফাংশন থাকতে হবে। একবার সমস্যা পাওয়া গেলে,

ত্রুটিপূর্ণ ঠিকানা ইউনিটটি অতিরিক্ত ঠিকানা ইউনিটের অপ্রয়োজনীয় মেমরিতে ম্যাপ করা যেতে পারে এবং সনাক্ত করা ত্রুটি ঠিকানাটি বাতিল করা হবে। বর্জন করা এড়িয়ে চলুন

পুরো ব্যয়বহুল চিপ।

ছোট এমবেডেড মেমরি ব্লক পরীক্ষা করা অতিরিক্ত গেট বা নিয়ন্ত্রণ যুক্তির প্রয়োজনীয়তা দূর করে। উদাহরণস্বরূপ, ভেক্টর রূপান্তর পরীক্ষার কৌশল রূপান্তর করতে পারে

স্ক্যান মোডের একটি সিরিজে কার্যকরী মোড।

BIST পদ্ধতির বিপরীতে, বাইপাস মেমরি ব্লকের কার্যকরী ইনপুট অতিরিক্ত যুক্তির প্রয়োজন হয় না। কারণ কোন অতিরিক্ত পরীক্ষার যুক্তির প্রয়োজন নেই, SoC

উন্নয়ন প্রকৌশলী অতীতে গঠিত পরীক্ষার নিদর্শন পুনরায় ব্যবহার করতে পারেন।

উন্নত ATPG সরঞ্জামগুলি শুধুমাত্র সমান্তরালভাবে ম্যাক্রোগুলি পরীক্ষা করে না বরং বিরোধ আছে কিনা তাও নির্ধারণ করে, পাশাপাশি কোন ম্যাক্রোগুলি সমান্তরালভাবে পরীক্ষা করা যেতে পারে এবং কোনটি বিশদ বিবরণ দেয়।

ম্যাক্রো সমান্তরালভাবে পরীক্ষা করা যাবে না। উপরন্তু, ম্যাক্রো ঘড়িটি স্ক্যান ঘড়ির (যেমন সিঙ্ক্রোনাস মেমরি) সমান হলেও এই ম্যাক্রোগুলি কার্যকরভাবে পরীক্ষা করা যেতে পারে।

বর্তমানে, ঘন দ্বি-পার্শ্বযুক্ত বোর্ডে পর্যাপ্ত পরীক্ষার পয়েন্ট নেই এবং প্রতিটি জটিল চিপ অবশ্যই একটি বাউন্ডারি স্ক্যান সার্কিট দিয়ে সজ্জিত করা উচিত। ছাড়া

বাউন্ডারি স্ক্যান, বোর্ড-লেভেল ম্যানুফ্যাকচারিং ডিফেক্ট লুকআপ বেশ কঠিন এবং খুঁজেও পাওয়া যায় না। সীমানা স্ক্যান সহ, বোর্ড-স্তরের পরীক্ষা অত্যন্ত সহজ

এবং চিপের মধ্যে লজিক সার্কিটরি থেকে স্বাধীন। বাউন্ডারি স্ক্যান উৎপাদনের যেকোনো পর্যায়ে চিপের স্ক্যান চেইনে ATPG মোডকে কনফিগার করতে পারে।